Test Chip 1

Diseño, fabricación y validación del chip TC1

Diseño físico del chip

El chip TC1 ha sido diseñado y fabricado utilizando la tecnología Intel 3, uno de los nodos más avanzados disponibles. Dado que esta tecnología no estaba accesible para entidades externas durante la fase de diseño, el BSC llevó a cabo sus evaluaciones internas empleando un nodo tecnológico comparable (TSMC N7), lo que permitió validar la calidad, viabilidad y robustez del código RTL antes de su implementación final por parte de Intel.

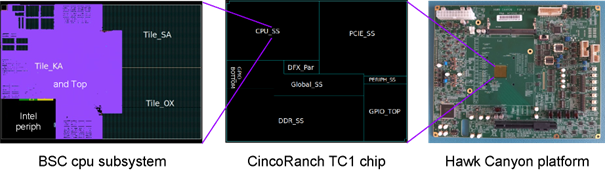

El diseño integra una arquitectura heterogénea basada en tres teselas independientes, cada una con un procesador diferente: Sargantana, Lagarto Ka con acelerador vectorial (VPU) y Lagarto Ox. A lo largo del proceso, el BSC realizó múltiples síntesis exploratorias para evaluar área y temporización, trabajando en estrecha coordinación con Intel para identificar y corregir aspectos críticos del diseño.

Como resultado, el subsistema de CPU (CPUSS) ocupa 3,2 mm² dentro de un chip completo de 15,2 mm², que incluye además periféricos e interfaces de alta velocidad como PCIe Gen5 y DDR5. El trabajo realizado sienta una base sólida para futuras arquitecturas de alto rendimiento y bajo consumo desarrolladas en el marco del proyecto.

Floorplan del chip completo (centro), Floorplan del CPUSS (izquierda); Fotografía del chip físico en la placa Hawk Canyon (derecha).

Bring-up

Construcción de placa, puesta en marcha del chip y evaluación

La puesta en marcha experimental (bring-up) del chip TC1 se realizó utilizando la placa de evaluación Hawk Canyon V2, diseñada y fabricada por Intel específicamente para la validación post-silicio del chip. Esta plataforma de altas prestaciones proporciona soporte completo para pruebas de hardware, desarrollo de firmware y depuración, incluyendo memoria DDR5, interfaces PCIe Gen5, y mecanismos avanzados de configuración y depuración.

A principios de 2025, el BSC recibió un primer lote de placas y llevó a cabo la formación y preparación del entorno de laboratorio para el montaje y configuración del sistema. En mayo de 2025 se logró con éxito el arranque de Linux en el chip TC1, validado inicialmente por Intel y posteriormente reproducido en los laboratorios del BSC.

En julio de 2025 se recibió un lote de 500 chips TC1, iniciándose las tareas sistemáticas de caracterización y validación. Los resultados mostraron una alta tasa de funcionalidad, con la gran mayoría de chips arrancando correctamente los tres procesadores integrados. Asimismo, se comprobó experimentalmente que el chip puede operar hasta 1,25 GHz, superando ampliamente las estimaciones conservadoras realizadas durante la fase de diseño.

Durante los meses siguientes se llevó a cabo la caracterización eléctrica, midiendo consumo y temperatura bajo distintas condiciones de funcionamiento, así como las primeras pruebas funcionales mediante la ejecución de benchmarks sobre los distintos procesadores. Estas actividades permiten evaluar el comportamiento real del chip y constituyen la base para el análisis detallado de prestaciones y la optimización del software asociado.

El bring-up del TC1 confirma la robustez del diseño y la viabilidad de la arquitectura, marcando un hito clave en la validación experimental del chip desarrollado en el marco del proyecto.

Comprobación experimental del chip TC1 en la placa Hawk Canyon.