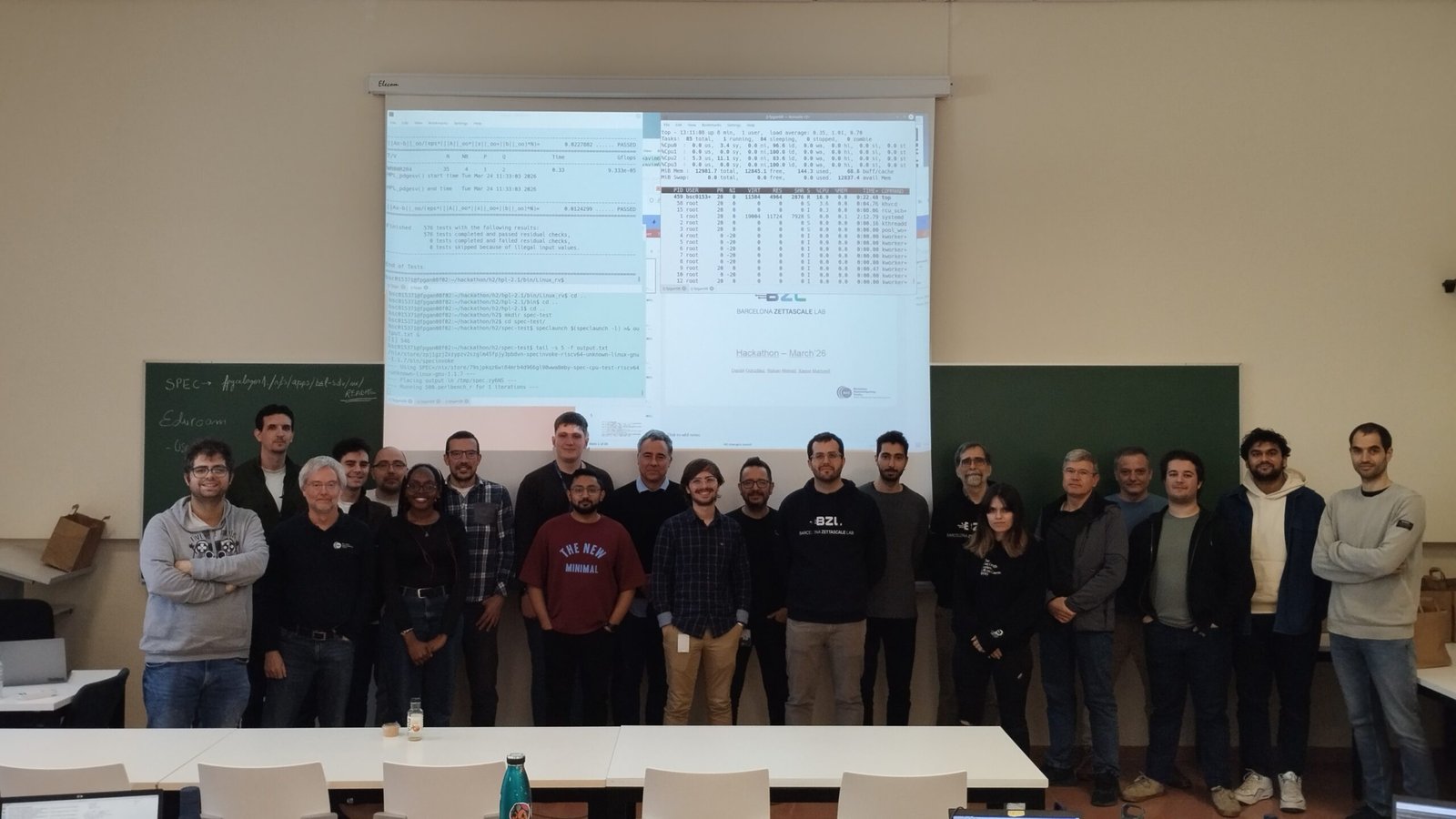

El 24 de marzo, el equipo BZL concluyó con éxito su segundo hackathon interno, titulado “Bring Your Code”, marcando un nuevo hito en los esfuerzos del proyecto por avanzar en la computación de alto rendimiento (HPC) sobre plataformas RISC-V.

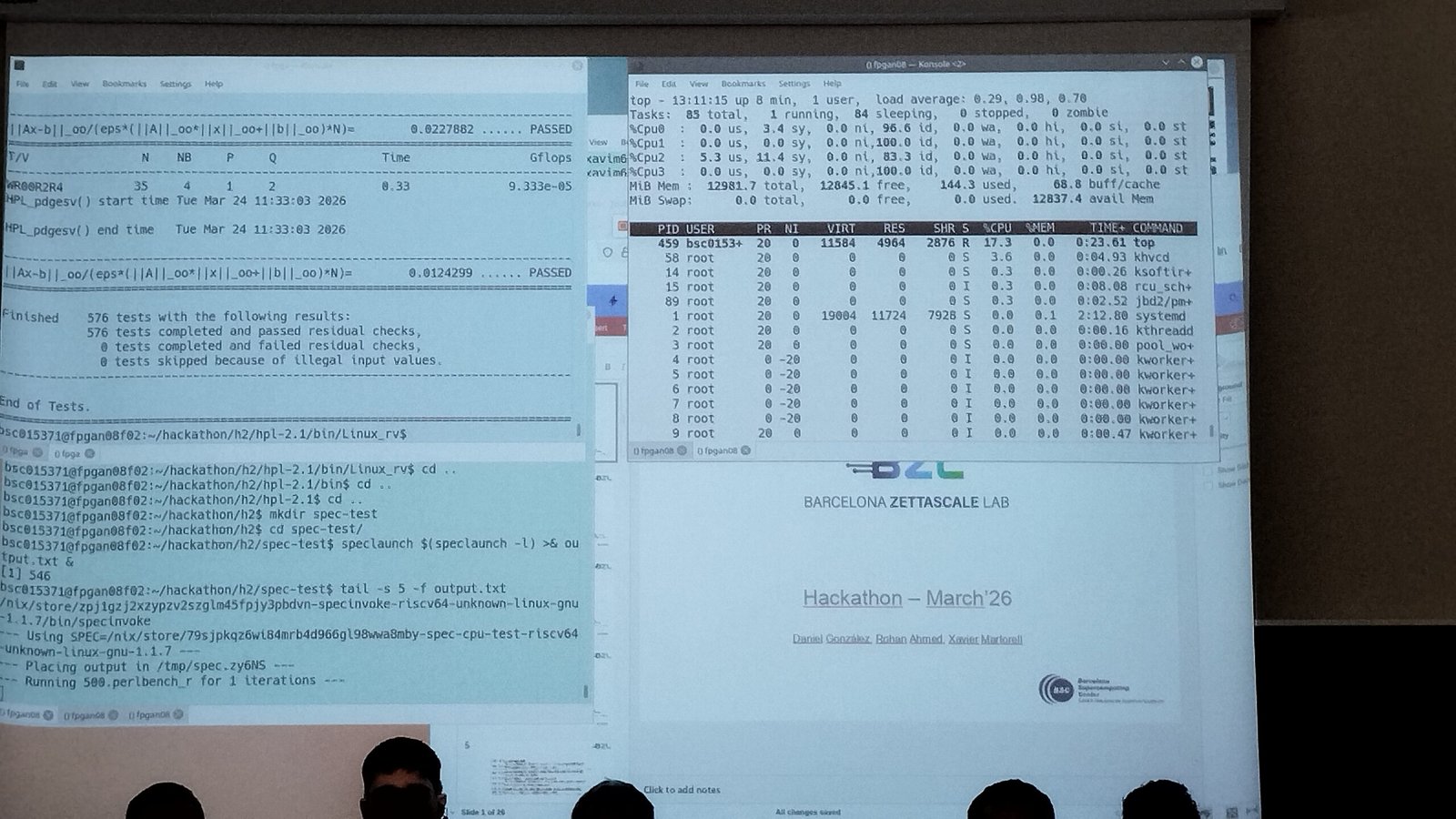

Sobre la base de los logros del primer hackathon, el evento tuvo como objetivo validar y perfeccionar el uso de sistemas RISC-V para cargas de trabajo computacionales exigentes. Durante el primer hackathon, los participantes demostraron la viabilidad de ejecutar cargas HPC en arquitecturas RISC-V, incluyendo ejecuciones multinúcleo y multinodo mediante benchmarks LINPACK basados en MPI. Estos primeros resultados proporcionaron información valiosa sobre el rendimiento del sistema, las herramientas y la experiencia de usuario en general, al tiempo que pusieron de relieve áreas clave de mejora como la conectividad FPGA, los flujos de compilación cruzada, los entornos preconfigurados y el rendimiento del procesamiento vectorial.

La segunda edición se centró en evaluar y estabilizar la pila de software SDV en las plataformas TC2 y Komodo. Los participantes accedieron al sistema a través de nodos de acceso dedicados y recursos FPGA reservados, probando configuraciones de doble núcleo Lagarto Ox sin soporte vectorial y configuraciones de un solo núcleo mejoradas con una Unidad de Procesamiento Vectorial (VPU). El entorno de software combinó OpenSBI, un kernel de Linux y sistemas de archivos raíz basados en Buildroot, con soporte para distribuciones como Ubuntu y Debian.

Una mejora clave fue la introducción de la partición “single”, que permite la asignación independiente de FPGA. Esto aumentó la flexibilidad, redujo la contención de recursos y permitió una experimentación más eficiente.

Los resultados confirmaron que las plataformas RISC-V pueden gestionar cargas de trabajo HPC y de benchmarking realistas, incluyendo ejecuciones MPI tanto en un solo nodo como distribuidas. Las mejoras en la infraestructura -especialmente la asignación de FPGA por usuario- mejoraron significativamente la usabilidad y los flujos de trabajo.

A pesar de estos avances, el hackathon también puso de manifiesto que el ecosistema aún se encuentra en una fase de maduración. El principal desafío identificado fue la inestabilidad y el rendimiento limitado de las configuraciones con VPU, lo que actualmente restringe el uso efectivo de aplicaciones vectorizadas.

En conjunto, el segundo hackathon “Bring Your Code” representa un paso significativo para posicionar RISC-V como una arquitectura viable para casos de uso de HPC, al tiempo que establece una hoja de ruta clara para futuras mejoras e innovación.