Test Chip 1

Design, manufacturing and validation of the TC1 chip

Physical Chip Design

The TC1 chip was designed and manufactured using Intel Technology 3, one of the most advanced nodes available. Since this technology was not accessible to external entities during the design phase, the BSC conducted its internal evaluations using a comparable technology node (TSMC N7), which allowed it to validate the quality, feasibility, and robustness of the RTL code before its final implementation by Intel.

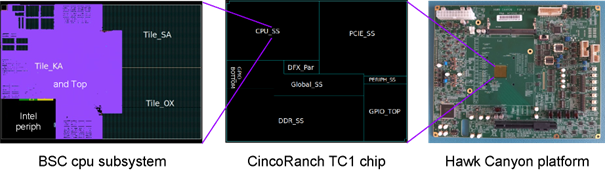

The design integrates a heterogeneous architecture based on three independent tiles, each with a different processor: Sargantana, Lagarto Ka with vector accelerator (VPU), and Lagarto Ox. Throughout the process, the BSC performed multiple exploratory syntheses to evaluate area and timing, working closely with Intel to identify and correct critical design aspects.

As a result, the CPU subsystem (CPUSS) occupies 3.2 mm² within a total chip of 15.2 mm², which also includes high-speed peripherals and interfaces such as PCIe Gen5 and DDR5. The work done lays a solid foundation for future high-performance, low-power architectures developed within the framework of the project.

Floorplan of the complete chip (center), Floorplan of the CPUSS (left); Photograph of the physical chip on the Hawk Canyon board (right).

Bring-up

Board Construction, Chip Setup, and Evaluation

The experimental bring-up of the TC1 chip was performed using the Hawk Canyon V2 evaluation board, designed and manufactured by Intel specifically for post-silicon validation of the chip. This high-performance platform provides comprehensive support for hardware testing, firmware development, and debugging, including DDR5 memory, PCIe Gen5 interfaces, and advanced configuration and debugging mechanisms.

In early 2025, the BSC received an initial batch of boards and carried out training and preparation of the laboratory environment for system assembly and configuration. In May 2025, Linux was successfully booted on the TC1 chip, initially validated by Intel and subsequently reproduced in the BSC laboratories.

In July 2025, a batch of 500 TC1 chips was received, and systematic characterization and validation tasks began. The results showed a high success rate, with the vast majority of chips successfully booting all three integrated processors. Furthermore, it was experimentally verified that the chip can operate at up to 1.25 GHz, significantly exceeding the conservative estimates made during the design phase.

Over the following months, electrical characterization was carried out, measuring power consumption and temperature under various operating conditions, as well as the first functional tests by running benchmarks on the different processors. These activities allow for the evaluation of the chip’s real-world performance and form the basis for detailed performance analysis and the optimization of the associated software.

The TC1 bring-up confirms the robustness of the design and the viability of the architecture, marking a key milestone in the experimental validation of the chip developed within the framework of the project.

Experimental verification of the TC1 chip on the Hawk Canyon board.