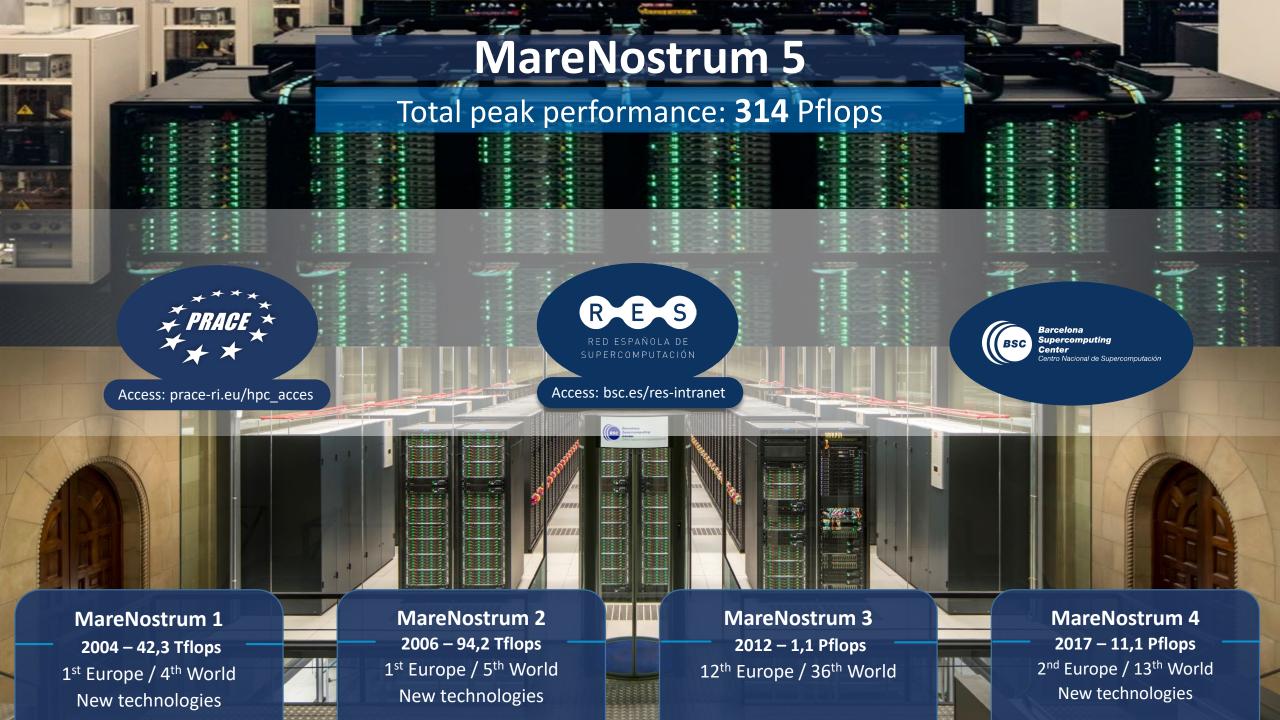

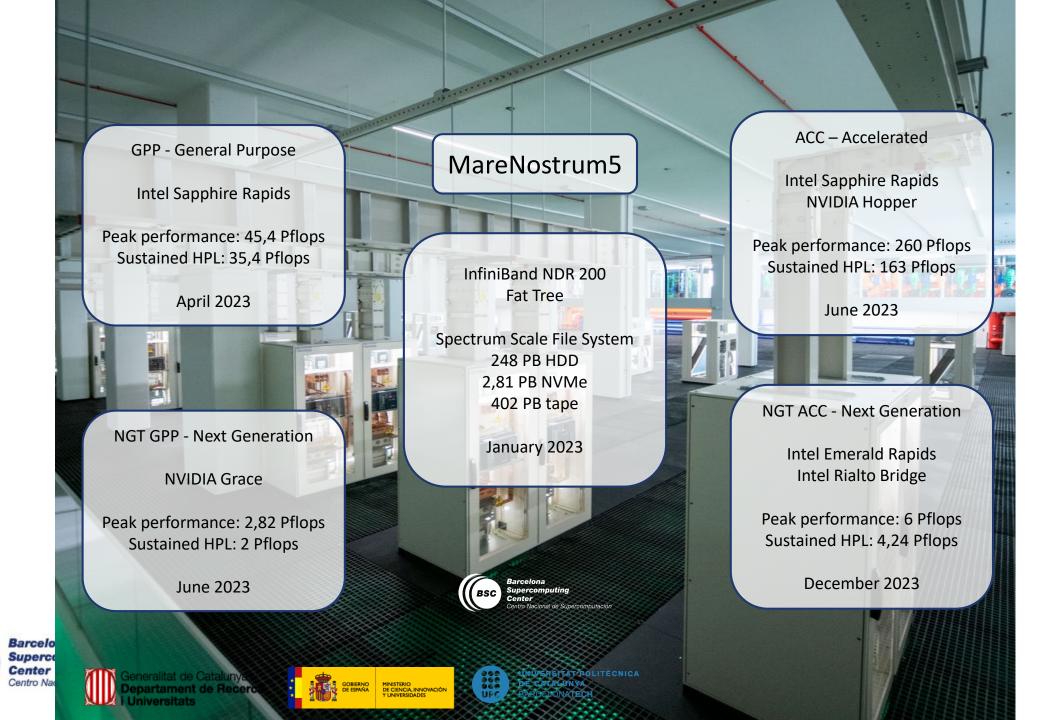

## Designing High Performance Computers at the Barcelona Supercomputing Center

Rafael Gomà BSC

BSC, Barcelona (Spain)

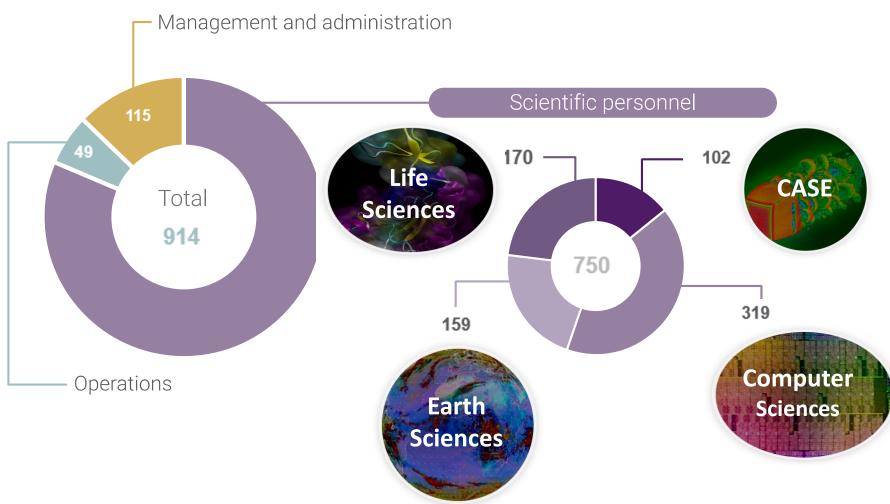

### **BSC** in numbers

#### People

## **HPC Today**

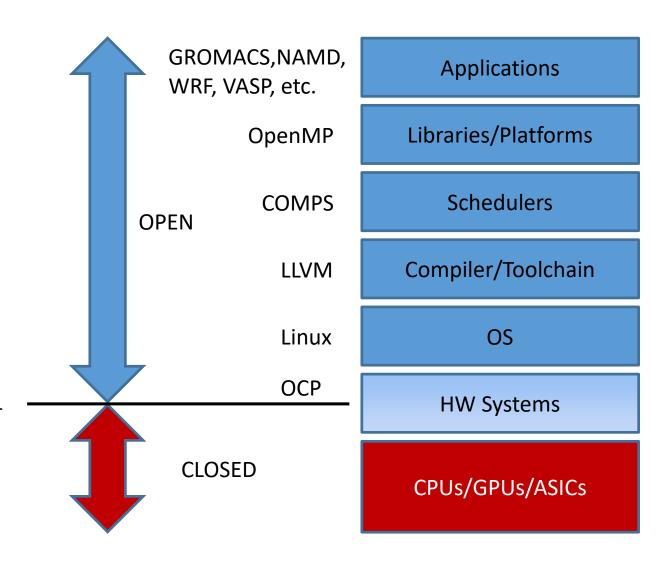

- Europe has led the way in defining a common open HPC software ecosystem

- Linux is the de facto standard OS despite proprietary alternatives

- Software landscape from Cloud to IoT already enjoys the benefit of open source

- Open source provides:

- A common platform, specification and interface

- Accelerates building new functionality by leveraging existing components

- Lowers the entry barrier for others to contribute new components

- Crowd-sources solutions for small and larger problems

- What about Hardware and in particular, the CPU?

#### RISC-V is an Open Standard Instruction Set Architecture (ISA)

Software uses the ISA to tell the hardware what to do.

At the base level, the RISC-V ISA and extensions ratified by RISC-V International are royalty free and open base building blocks for anyone to build their own solutions and services on.

RISC-V International is the global non-profit home of the open standard RISC-V ISA, related specifications, and stakeholder community

# RISC-V is rapidly building the strongest ecosystem

## RISC-V instrumented with software top of mind

Toolchain and OS support required for Extension ratification

Single hypervisor standard to simplify and unify application support

Thousands of software developers bringing workloads to RISC-V

**Strategic imperative and investment** by commercial sector and geographies

**Modern design approaches** leveraged for fewer instructions

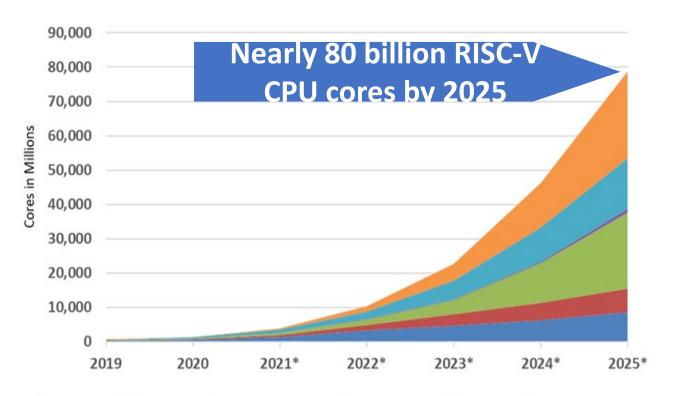

# RISC-V CPU core market grows 114.9% CAGR, capturing >14% of all CPU cores by 2025

## ■ Computer ■ Consumer ■ Communications ■ Transportation ■ Industrial ■ Other RISC-V Barcelona Supercomputing Conter 8

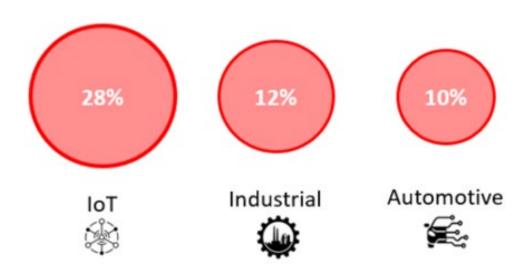

#### RISC-V Penetration Rate by 2025

"The rise of RISC-V cannot be ignored... RISC-V will shake up the \$8.6 Billion semiconductor IP market."

-- William Li, Counterpoint Research

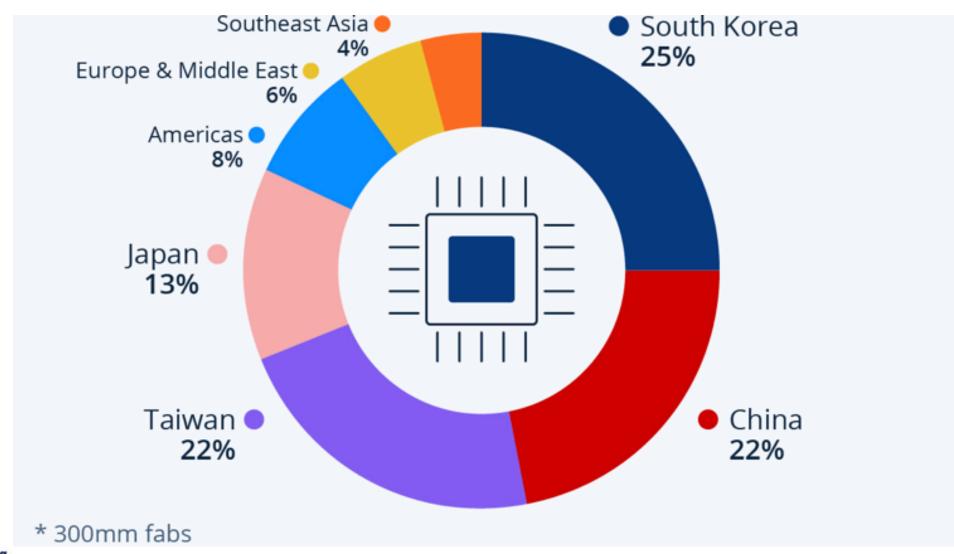

### WW Semiconductors market

## Microprocessor Technology: Strategy

EU goal: autonomy in strategic processing technologies

#### Our **ambition**: by 2030

- The production of cutting-edge and sustainable semiconductors in Europe including processors is at least 20% of world production in value

- Manufacturing capacities below 5nm nodes aiming at 2nm

- Energy efficiency 10X more than today

✓ RISC-V ISA plays a central role on EU's technology strategy

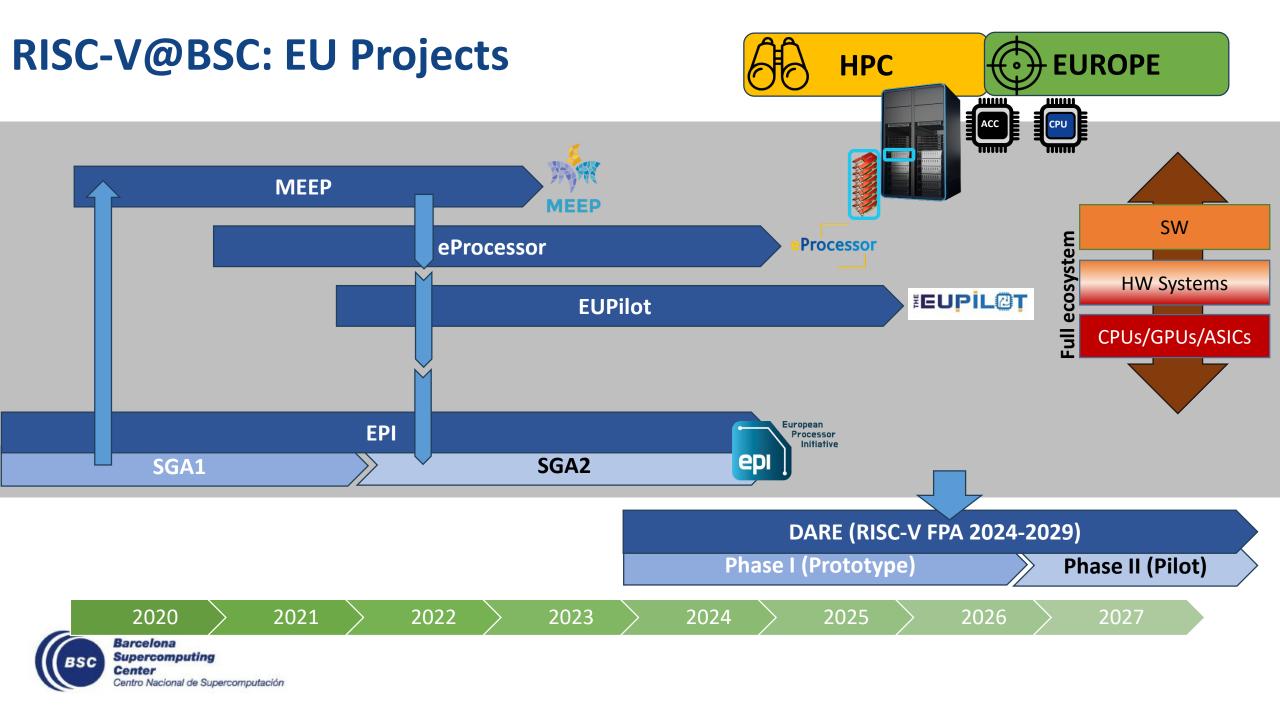

## The European Processor Initiative

The European Processor Initiative (EPI) under the SGA1 of the Framework Partnership Agreement (FPA: 800928), to design and implement a roadmap for a new family of low-power European processors for extreme scale computing, high-performance Big-Data and a range of emerging applications.

- History: Remember MontBlanc? BSC leads the RISC-V HPC accelerator development

- Consortium (SGA1):

- 28 partners from 10 European countries to Coordinate: Bull SAS (France)

- Budget: €80M (100% funded)

- Duration: 36 months (01/12/2018-31/12/2021)

- 5 Streams (4 Technical and 1 Management/Exploitation/C&D)

#### **EPI MAIN OBJECTIVE**

To develop European microprocessor and accelerator technology

Strengthen competitiveness of EU industry and science

SiPearl

Rhea

Arm-based general purpose CPU

**EPAC**

RISC-V based Accelerators

BSC, SemiDynamics, EXTOLL, FORTH, ETHZ, UniBo, UniZG, Chalmers, CEA, E4, Menta, ZPT, ...

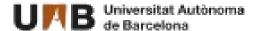

## **DRAC Project**

• **DRAC**: **D**esigning **R**ISCV-based **A**ccelerators for next generation **C**omputers

- Consortium: BSC (coord.), UPC, UAB, UB, URV

- Dates: June 2019 June 2023

- <u>Budget</u>: 4M€ (50% co-funded by Generalitat)

- Alignment with the European Processor Initiative (EPI) project:

- Focus on RISC-V-based accelerator developed in Barcelona

- Promote RISC-V in the CS degrees in Catalan universities

- Build IC design teams capable of taping out DRAC technology: RTL design, verification and physical design

### **Lagarto RISC-V Tapeouts**

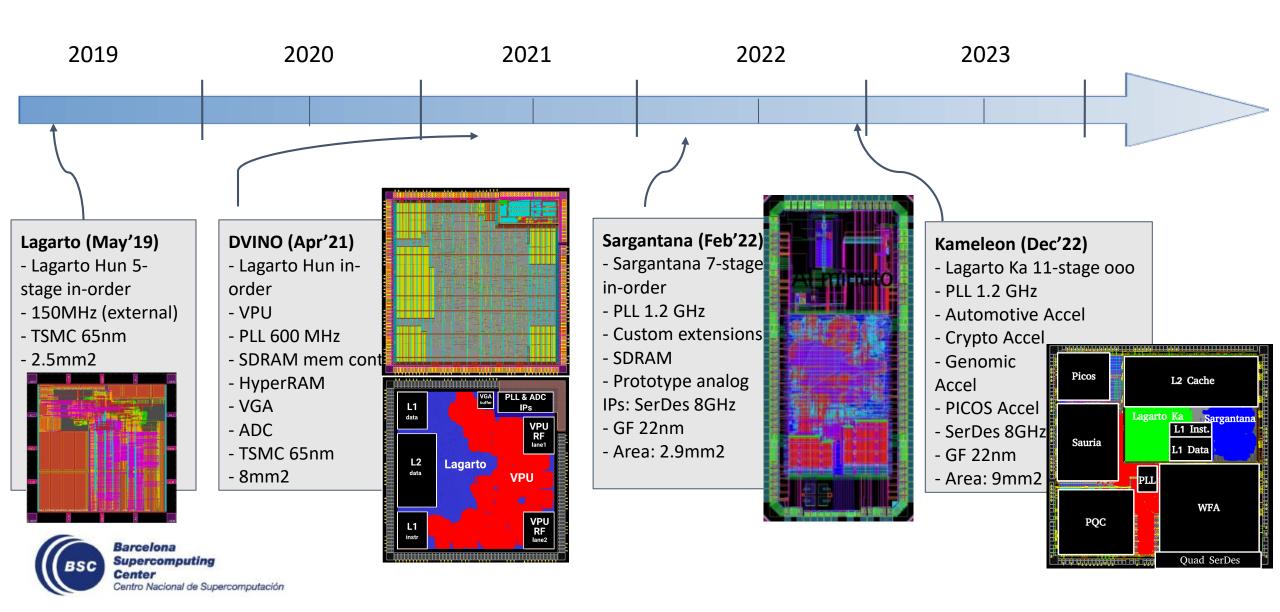

## First Steps Towards a Lagarto Multicore

- Multicore design based on:

- DVINO processor

- RISC-V ISA support: I, M, A,

F, D, C, V

- 4-lane VPU

- OpenPiton 2-level cache hierarchy (priv. L1, shared L2)

- Current status

- Linux boot (openSBI)

- RTL simulation of parallel applications (up to 64 cores)

- Multiple memory controllers

- FPGA-ready

- Integrating Ka+VPU

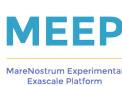

## Towards a RISC-V Heterogeneous Manycore

Other Domain-Specific Accelerator Tiles (sparse, security, safety, etc.)

#### **EUROPEAN CHIPS ACT**

The European Chips Act will ensure that the EU strengthens its semiconductors ecosystem, increases its resilience, as well as ensure supply and reduce external dependencies.

1. Strengthen Europe's research and technology leadership towards smaller and faster chips

2. Build and reinforce capacity to innovate in the design, manufacturing and packaging of advanced chips

3. Put in place a framework to increase production capacity to 20% of the global market by 2030

4. Address the skills shortage, attract new talent and support the emergence of a skilled workforce

5. Develop an in-depth understanding of the global semiconductor supply chains

The Chips Act should result in additional public and private investments of more than €15 billion.

These investments will complement:

- existing programmes and actions in research & innovation in semiconductors (Horizon Europe, Digital Europe programme)

- announced support by Member States.

In total, more than €43 billion of policy-driven investment will support the Chips Act until 2030, which will be broadly matched by long-term private investment.

## 3. EXECUTION ACTIONS & BUDGET (I)

|                                                                                                                  | M€        |

|------------------------------------------------------------------------------------------------------------------|-----------|

| COMPONENT I. BOLSTERING SCIENTIFIC CAPACITY                                                                      | 1.165     |

| <b>ACTION 1:</b> Development of R&D&i on cutting-edge and alternative architecture microprocessors               | 475       |

| ACTION 2: Development of R&D&i on integrated photonics                                                           | 150       |

| ACTION 3: Development of R&D&i on quantum chip development                                                       | 40        |

| <b>ACTION 4:</b> Budget line for the IPCEI on Microelectronics and Communication Technologies                    | 500       |

| COMPONENT II. DESIGN STRATEGY                                                                                    | 1.33<br>0 |

| <b>ACTION 5:</b> Creation of cutting-edge alternative architecture microprocessor fabless companies              | 950       |

| ACTION 6: Creation of pilot lines                                                                                | 300       |

| <b>ACTION 7:</b> Creation of a network for education, training and skills-building in relation to semiconductors | 80        |

## 3. EXECUTION ACTIONS & BUDGET (II)

|                                                                         | M€    |

|-------------------------------------------------------------------------|-------|

| COMPONENT III. CONSTRUCTION OF FABRICATION PLANTS IN SPAIN              | 9.350 |

| <b>ACTION 8:</b> Creating fabrication capacity at sizes below 5 nm      | 7.250 |

| <b>ACTION 9:</b> Creating fabrication capacity at sizes above 5 nm      | 2.100 |

|                                                                         |       |

| COMPONENT IV. STIMULATING THE ICT MANUFACTURING INDUSTRY IN SPAIN       | 400   |

| <b>ACTION 10:</b> ICT manufacturing industry incentive scheme           | 200   |

| ACTION 11: Creation of a chips fund                                     | 200   |

|                                                                         |       |

| GOVERNANCE                                                              | 5     |

| Special Commissioner for the Microelectronic and Semiconductors Project | 5     |

TOTAL PUBLIC INVESTMENT

12.250

### Intel Labs Barcelona are back!

- New joint Intel BSC Laboratory to design HPC processors based on RISC-V technology

- Funding: 400M\$ in the next 10 years. <u>Headcount</u>: ~200 (estimated)

Other companies will also come to Spain!

#### Path to Zettascale

Developing European Hardware/Software

Technology

Full Stack Open Source HPC Ecosystem

Build Full System based on RISC-V: MN6 and many others

European & Global collaboration

Intel and BSC: Continuing to collaborate into

the Zettascale era

Research & Product

Announced at ISC in June 2022

## BSC is building a New Lab! 100+ Job Opportunities

Research Engineer/Researcher

**R&D** for Zettascale and beyond: Applications to Accelerators

If your experience and/or motivation include any of the disciplines and skills below, check out our QR:

**Hardware** (Processor architecture, micro-architecture, accelerators, memory hierarchy, memory controllers, HBM, DRAM, non-volatile memory, RTL design, VHDL, verilog, SystemC, System verilog, Synopsys, Cadence, Mentor Graphics, synthesis, place and route, timing closure, packaging, PCB design, verification, validation, CI, post-silicon debug, DFT, gate-level simulation,...)

**Software** (programming models, MPI, compilers (LLVM), SYCL, OneAPI, Tensorflow, PyTorch, Apache Spark, CI/CD, operating systems, managed runtimes, OpenMP, task-based programming models, containers, security, fault-tolerance, virtualization, C/C++, Tcl, Python, Perl/Csh,...)

**Reference:** 176\_23\_CS\_Z\_R0-4-RE1-4

### Spanish Open Hardware Alliance

29 Universities and 3 research centers are partnering to share proposals and collaborate to take advantage of the opportunity raised by the global adoption of the RISC-V standard.

Also, establishing bridges with related industry associations like AESEMI

Without universities, there is nor talent neither chips!