On March 24, the BZL team successfully concluded its second internal hackathon, titled “Bring Your Code,” marking another milestone in the project’s efforts to advance high-performance computing on RISC-V platforms.

Building on the achievements of the first hackathon, the event aimed to validate and refine the use of RISC-V systems for demanding computational workloads. During the first hackathon, participants demonstrated the feasibility of running HPC workloads on RISC-V architectures, including multi-core and multi-node execution through MPI-based LINPACK benchmarks. These early results provided valuable insights into system performance, tooling, and overall user experience, while highlighting key areas for improvement such as FPGA connectivity, cross-compilation workflows, preconfigured environments, and vector processing performance.

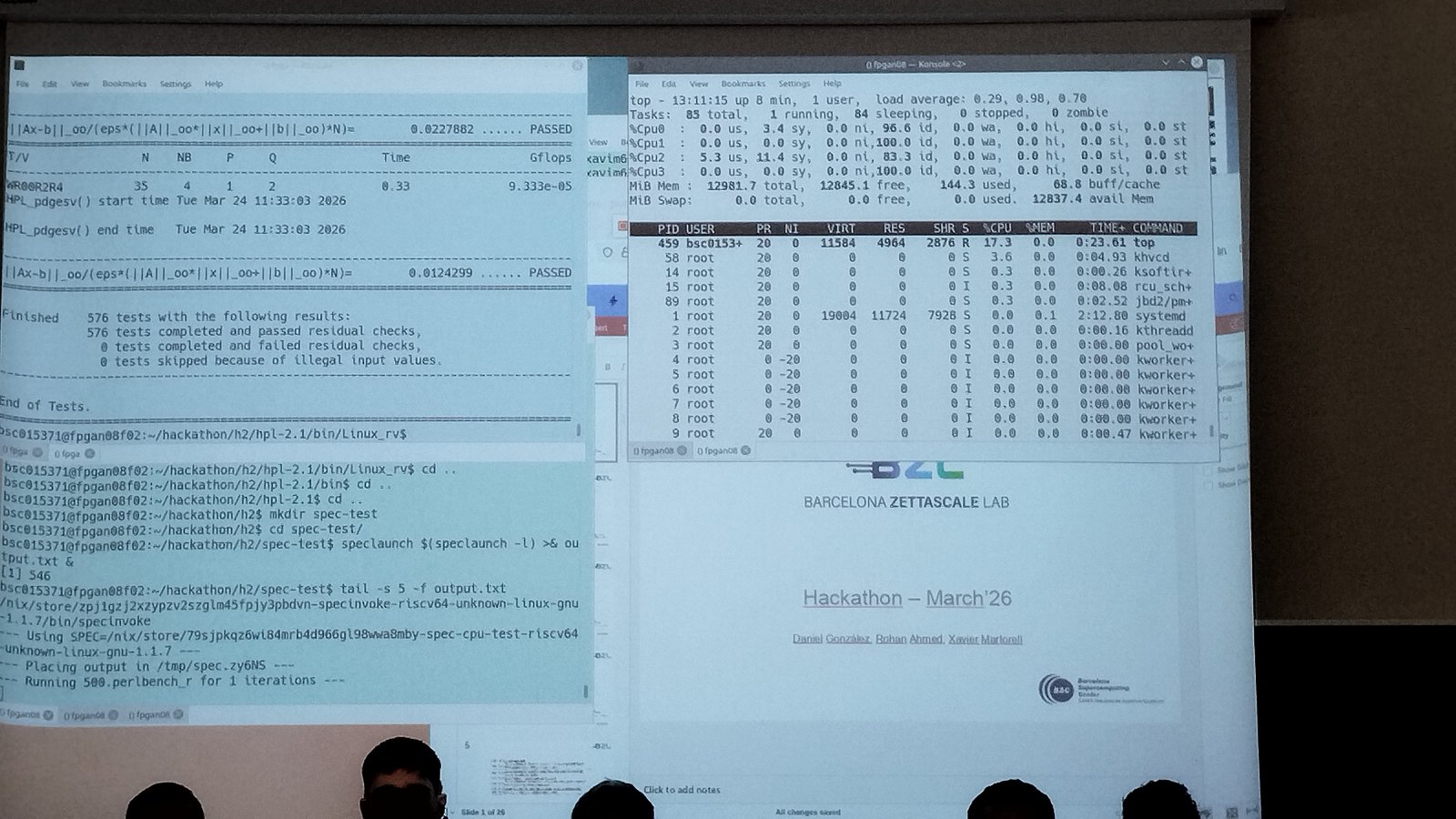

The second edition focused on evaluating and stabilizing the SDV software stack on TC2 and Komodo platforms. Participants accessed the system via dedicated login nodes and reserved FPGA resources, testing dual-core Lagarto Ox setups without vector support and single-core configurations enhanced with a Vector Processing Unit (VPU). The software environment combined OpenSBI, a Linux kernel, and Buildroot-based root file systems, with support for distributions such as Ubuntu and Debian.

A key improvement was the introduction of the “single” partition, allowing independent FPGA allocation. This increased flexibility, reduced resource contention, and enabled more efficient experimentation.

Results confirmed that RISC-V platforms can handle realistic HPC and benchmarking workloads, including single-node and distributed MPI executions. Infrastructure upgrades—especially per-user FPGA allocation—significantly improved usability and workflows.

Despite this progress, the hackathon also underscored that the ecosystem remains in a maturation phase. The most pressing challenge identified was the instability and limited performance of VPU-enabled configurations, which currently restrict effective use of vectorized applications.

Overall, the second “Bring Your Code” hackathon represents a significant step forward in positioning RISC-V as a viable architecture for HPC use cases, while establishing a clear roadmap for ongoing improvements and innovation.